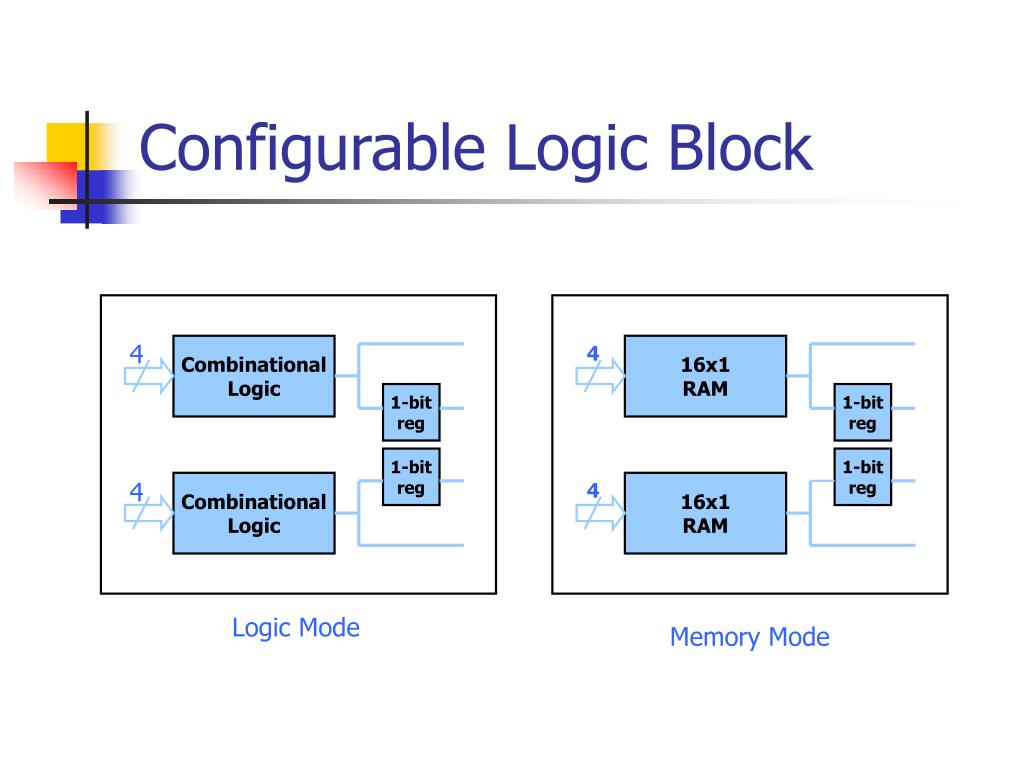

The basic building block of the FPGA is the Look Up Table based function generator. LUT implements the combinational logical functions the MUX is used for selection logic, and D flip flop stores the output of the LUT Logic Block contains MUX (Multiplexer), D flip flop and LUT.

They are I/O blocks or Pads, Switch Matrix/ Interconnection Wires and Configurable logic blocks (CLB). The general FPGA architecture consists of three types of modules. Therefore, these are used in VLSI based projects for electronic engineering students. FPGAs are some of the new trending areas of VLSI. This article describes about theFPGA basics and FPGA architecture module that includes I/O pad, logic blocks and switch matrix. But, FPGAs are fabricated in less than a second,the cost will be from a few dollars to a thousand dollars.The flexible nature of the FPGA comes at a significant costin area, power consumption and delay.When compared to a standard cell ASIC, an FPGA requires 20 to 35 times more area, and the speed’s performance will be 3 to 4 times slower than the ASIC. Normally, ASICs takes months to manufacture and the cost of them will be thousands of dollars to obtain the device. 650–665, May2012.FPGAs can provide a number of advantages over a fixed function ASIC technology such as standard cells. Cortés, “Dynamic tolerance region computing for multimedia,” IEEE Trans. Valero, “Fuzzy memoization for floatingpoint multimedia applications,” IEEE Trans. Stack (WACAS), Salt Lake City, UT, USA, 2014. Paul, “iACT: A softwarehardware framework for understanding the scope of approximate computing,” in Proc. Mehrez, “Efficient tree topology for fpga interconnect network,” in ACM Great Lakes Symposium on VLSI, 2008, pp. Yu, “Directional and singledriver wires in fpga interconnect,” in IEEE Conference on FPT, 2004,pp. Rose, “VPR: A New Packing Placement and Routing Tool for FPGA research,” International Workshop on FPGA, pp. Mehrez, “ASIF: Application Specific Inflexible FPGA,” in International Conference on Field- Programmable Technology, 2009.

#FPGA LUT TO ASIC GATES VERIFICATION#

Tharmalignam, “Equivalence Verification of FPGA and Structured ASIC Implementations,” August 2007, pp. Maeda, “Design Methodology and Tools for NEC Electronics Structured ASIC,” April 2004, pp. Tsai, “Structured ASIC, Evolution or Revolution,” April 2004, pp. Rose, “Measuring the gap between FPGAs and ASICs,” in Proceedings of the 2006 ACM/SIGDA 14th international symposium on Field programmable gate arrays. Hardened multiplexers are evaluated toward the goal of higher logic density and area reduction. Hybrid configurable logic block architectures for field programmable gate arrays that contain a mixture of lookup tables and hardened multiplexers are evaluated toward the goal of higher logic density and area reduction. Compared with most prior works on approximate computing, which target approximate processors and arithmetic blocks. Approximate computing is one promising method for achieving energy efficiency. Crossref, Abstract:įield programmable gate arrays (FPGAs) are increasingly used as the computing platform for fast and energy efficient execution of recognition, mining, and search applications. E.Ganesan and V.Sakthivel, "A Novel FPGA Design with Hybrid LUT / MUX Architecture," SSRG International Journal of Electronics and Communication Engineering, vol.

0 kommentar(er)

0 kommentar(er)